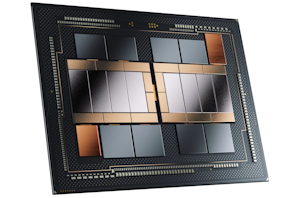

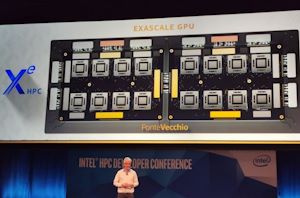

Ponte Vecchio

Intel this week has started production at Fab 9, the company's latest and most advanced chip packaging plant. Joining Intel's growing collection of facilities in New Mexico, Fab 9 is tasked with packaging chips using Intel's Foveros technology, which is currently used to build the company's latest client Core Ultra (Meteor Lake) processors and Data Center Max GPU (Ponte Vecchio) for artificial intelligence (AI) and high-performance computing (HPC) applications. The fab near Rio Rancho, New Mexico, cost Intel $3.5 billion to build and equip. The high price tag of the fab – believed to be the single most expensive advanced packaging facility ever built – underscores just how serious Intel is regarding its advanced packaging technologies and production capacity. Intel's product roadmaps call for making...

TACC's Stampede3 Supercomputer Uses Intel's Xeon Max with HBM2E and Ponte Vecchio

The Texas Advanced Computing Center (TACC) unveiled its latest Stampede supercomputer for open science research projects, Stampede3. TACC anticipates that Stampede3 will come online this fall and will deliver...

5 by Anton Shilov on 7/25/2023The Aurora Supercomputer Is Installed: 2 ExaFLOPS, Tens of Thousands of CPUs and GPUs

Argonne National Laboratory and Intel said on Thursday that they had installed all 10,624 blades for the Aurora supercomputer, a machine announced back in 2015 with a particularly bumpy...

39 by Anton Shilov on 6/22/2023Supermicro Lists Intel Data Center GPU Max 'Ponte Vecchio' Based Machines

Supermicro this week began to list the industry's first commercial servers based on Intel's Data Center GPU Max 'Ponte Vecchio' compute GPUs. The machines use Ponte Vecchio in add-in-board...

1 by Anton Shilov on 5/4/2023Intel Scraps Rialto Bridge GPU, Next Server GPU Will Be Falcon Shores In 2025

On Friday afternoon, Intel published a letter by Jeff McVeigh, the company’s interim GM of their Accelerated Computing Systems and Graphics group (AXG). In it, McVeigh offered a brief...

47 by Ryan Smith on 3/4/2023Intel Unveils Rialto Bridge: Second-Gen Xe-HPC Accelerator to Succeed Ponte Vecchio

With ISC High Performance 2022 taking place this week in Hamburg, Germany, Intel is using the first in-person version of the event in 3 years to offer an update...

38 by Ryan Smith on 5/31/2022Intel: Sapphire Rapids With 64 GB of HBM2e, Ponte Vecchio with 408 MB L2 Cache

This week we have the annual Supercomputing event where all the major High Performance Computing players are putting their cards on the table when it comes to hardware, installations...

69 by Dr. Ian Cutress on 11/15/2021Intel's Aurora Supercomputer Now Expected to Exceed 2 ExaFLOPS Performance

As part of Intel’s 2021 Innovation event, the company offered a brief update on the Aurora supercomputer, which Intel is building for Argonne National Laboratory. The first of the...

14 by Ryan Smith on 10/27/2021Hot Chips 2021 Live Blog: Graphics (Intel, AMD, Google, Xilinx)

Welcome to Hot Chips! This is the annual conference all about the latest, greatest, and upcoming big silicon that gets us all excited. Stay tuned during Monday and Tuesday...

12 by Dr. Ian Cutress on 8/24/2021Hot Chips 33 (2021) Schedule Announced: Alder Lake, IBM Z, Sapphire Rapids, Ponte Vecchio

Once a year the promise of super hot potatoes graces the semiconductor world. Hot Chips in 2021 is set to be held virtually for the second successive year, and...

33 by Dr. Ian Cutress on 5/18/2021Intel Teases Ponte Vecchio Xe-HPC Power On, Posts Photo of Server Chip

In what’s turning into an Xe sort of day, Intel’s GPU guru and frontman for their GPU division, Raja Koduri, has tweeted that the company is getting ready to...

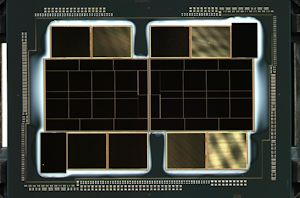

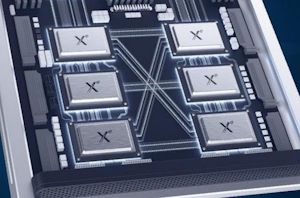

31 by Ryan Smith on 1/26/2021Intel Xe-HPC GPU Status Update: 4 Process Nodes Make 1 Accelerator

Continuing today’s GPU news from Intel’s Architecture Day presentation, on top of the Xe-LP architecture briefing and Xe-HPG reveal, the company has also offered a brief roadmap update for...

20 by Ryan Smith on 8/13/2020Analyzing Intel’s Discrete Xe-HPC Graphics Disclosure: Ponte Vecchio, Rambo Cache, and Gelato

It has been a couple of weeks since Intel formally provided some high-level detail on its new discrete graphics strategy. The reason for the announcements and disclosures centered around...

49 by Dr. Ian Cutress on 12/24/2019AnandTech Exclusive: An Interview with Intel’s Raja Koduri about Xe

This week Raja gave the keynote at Intel’s HPC DevCon event, a precursor to Supercomputing, and I did my usual thing of asking for the interview, fully expecting the...

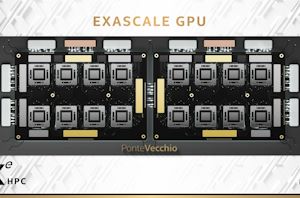

73 by Dr. Ian Cutress on 11/20/2019Intel’s 2021 Exascale Vision in Aurora: Two Sapphire Rapids CPUs with Six Ponte Vecchio GPUs

For the last few of years, when discussing high performance computing, it has been tough to avoid hearing the word ‘exascale’. Even last month, on 10/18, HPC twitter was...

43 by Dr. Ian Cutress on 11/17/2019Intel’s Xe for HPC: Ponte Vecchio with Chiplets, EMIB, and Foveros on 7nm, Coming 2021

Today is Intel’s pre-SC19 HPC Devcon event, and with Raja Koduri on stage, the company has given a small glimpse into its high-performance compute accelerator strategy for 2021. Intel...

16 by Dr. Ian Cutress on 11/17/2019