ASML to Deliver First High-NA EUV Tool This Year

by Anton Shilov on September 6, 2023 10:00 PM EST- Posted in

- Semiconductors

- Intel

- Micron

- SK Hynix

- ASML

- TSMC

- Samsung Foundry

- High-NA

- Intel 18A

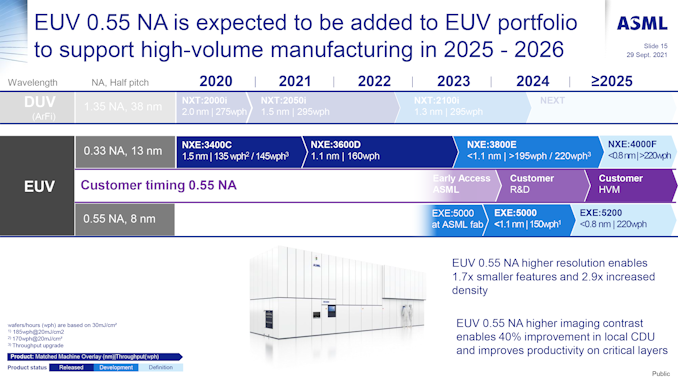

In a promising sign for the development of the next generation of EUV lithography machines, ASML has revealed that the company is set to deliver the industry's first High-NA extreme ultraviolet (EUV) lithography scanner by the end of the year. That machine, the 0.55 numerical aperture (NA) Twinscan EXE:5000 pilot scanner, is being developed for chipmakers so that they may learn how to efficiently use High-NA EUV technology. Following those R&D efforts, high volume manufacturing of chips using High-NA scanners expected to commence in 2025, when ASML begins shipping the commercial-grade Twinscan EXE:5200 scanner.

"A few suppliers had some difficulties in actually ramping up and also giving us the right level of technological quality, so that led to some delay," said ASML CEO Peter Wennink, in a brief interview with Reuters. "But in fact, the first shipment is still this year.

Currently, the most sophisticated EUV scanners in various fabs are ASML's Twinscan NXE:3400C and NXE:3400D. These scanners are equipped with 0.33 numerical aperture (NA) optics, delivering a 13 nm resolution. Such a resolution is suitable to print chips on manufacturing technologies featuring metal pitches between 30 nm and 38 nm. However, when pitches drop below 30 nm (at nodes beyond 5 nm), 13 nm resolution will not be enough and chipmakers will have to use EUV double patterning and/or pattern shaping technologies. Given that double patterning EUV can be both costly and fraught with risks, the industry is working on High-NA EUV scanners, which have a 0.55 NA, to achieve an 8nm resolution for manufacturing technologies intended for the latter half of the decade.

ASML's High-NA scanners will once again change configurations of semiconductor fabs as they will not only employ new optics, but will also need a new and bigger light source, which will require new fab structures leading to significant investments. Though ASML's High-NA scanners are expected to be significant investments themselves, with various reports pointing to $300 - $400 million per unit, up from over $200 million per 0.33 NA EUV scanner.

Intel had originally planned to use ASML's High-NA tools for its 18A (1.8 nm) production node, which was set for high-volume manufacturing in 2025, coinciding with ASML's anticipated delivery of its Twinscan EXE:5200. However, Intel later pulled in the commencement of its 18A production to the latter half of 2024, apparently opting to use ASML's Twinscan NXE:3600D/3800E with two exposures, as well as Applied Material's Endura Sculpta pattern-shaping system to reduce usage of EUV double patterning.

Intel is expected to be the alpha customer for ASML's pilot High-NA scanner, so when it receives the machine later this year, its developers and engineers will be able to adjust Intel's process technologies to the upcoming production tools. Given the timing of the tools versus Intel's own process node plans, for the moment it remains unknown just how and when they will integrate the tools into their processes. As 18A is expected to be a long-term node, Intel may still be intending to use High-NA EUV with it, even if that option isn't viable at the start.

Meanwhile, Samsung Foundry and TSMC are slated to start production of chips on their 2 nm-class nodes (SF2, N2) in late 2025. Though just how High-NA machines factor into their plans remains equally up in the air.

Source: Reuters

7 Comments

View All Comments

ABR - Thursday, September 7, 2023 - link

So Intel's catch-up and overtake is still on track, it sounds like.But 400 million per machine! More than a passenger jet aircraft. It starts to seem like selling the shovels for the shovels is really paying off.

Bwerngbong - Thursday, September 14, 2023 - link

ASML is a company employing a workforce of mechanical engineers, electrical engineers, solid state and optical physics speccialists and shit ton of codersIntel is a company that employs chip chip designers and other electrical engineers, solid state physicists and ECEs, and armies of process engineers.

the simple reality is that the complexity of *Design only* is already sufficiently high that Intel struggles to operate the "IP core level" the verilog level, the gate and register level tne manufacutring and wirebonding level, and the API/IDE development level.

AMD? NVidia? They dont even pretend to try to do all that shit. Neither does TSMC. They just stick to their blacksmithing and design chips... design chips... design chips.... or make chips... make chips.... wire bond wire bond.....

Sivar - Thursday, September 7, 2023 - link

"..the commercial-grade Twinscan EXE:5200 scanner."Is there a non-commercial-grade EUV scanner?

artifex - Thursday, September 7, 2023 - link

The article does say the 5000 this year is a "pilot" for R&D, before that one comes out.Holliday75 - Friday, September 8, 2023 - link

That is what I assumed as well.PeachNCream - Saturday, September 9, 2023 - link

Its an Anton article so there will always be that kind of nonsense. Just ignore it unless its especially awful.TristanSDX - Saturday, September 9, 2023 - link

Sure, R&D is such scanner. It have low throughput ,low uptime and other disadvantages. Presented scanner is R&D version