PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

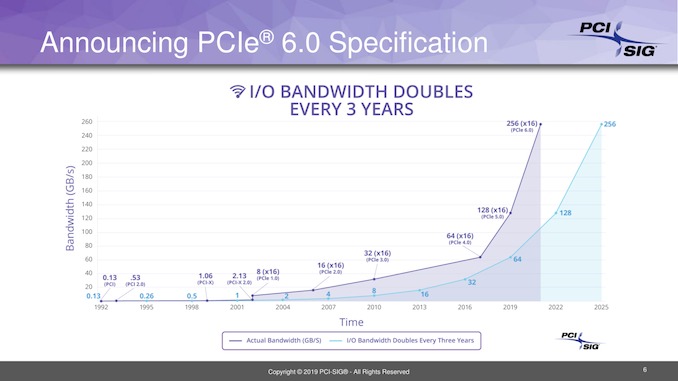

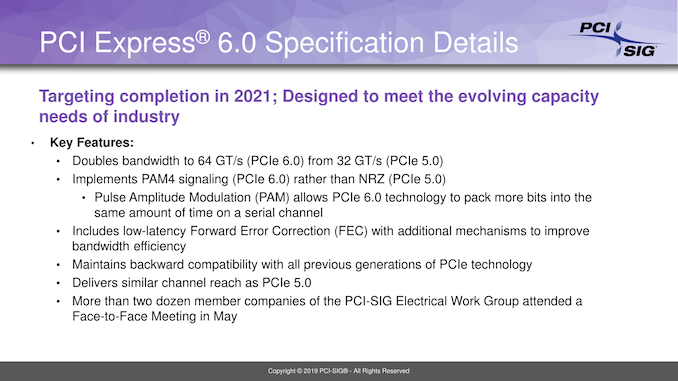

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

colinstu - Friday, February 21, 2020 - link

Wait... whatever happened to PCIe 5.0?fred666 - Friday, February 21, 2020 - link

was approved in 2019, and yet we have no sign of products supporting it anytime soon.PaulHoule - Friday, February 21, 2020 - link

It takes a long time to develop standards. Somewhere people are working on 6G wireless, but they aren't talking loudly about it because people are sick and tired of hearing about 5G even though it isn't here yet.Intel also takes a lot of blame for PCI4's slow rollout. All of the other high-performance chip vendors have moved on past PCI3, even Intel is rolling out PCI4 peripherals, but Intel-x86 support for PCI4 is still dead in the water.

HStewart - Friday, February 21, 2020 - link

I believe Intel decided to wait to PCI 5.0 for support. I would not blame it on Intel. The big question why is PCI coming out with these specifications so quickly - they are not the one that are actually doing the implementation.Has anybody actually determine what kind of hardware is required to pump out 64 GT/s.

sa666666 - Friday, February 21, 2020 - link

Of course you wouldn't blame it on Intel. Have you ever blamed Intel for anything, especially when they truly deserved it? Of course not.Qasar - Saturday, February 22, 2020 - link

ahh there it is, the positive hstewart intel spin, on something negitive against intel.i dont think he has EVER said anything bad about his beloved intel. even when others refute his positivity with proof.

Toadster - Friday, February 21, 2020 - link

Ice Lake Server 2020 https://en.wikichip.org/wiki/intel/microarchitectu...mode_13h - Friday, February 21, 2020 - link

Sapphire Rapids is slated to feature it, in 2021:https://www.tomshardware.com/news/intel-server-ddr...

Given that Intel's CXL shares common foundations with PCIe 5.0, it's a safe bet that Intel will follow-through on this.

PaulHoule - Friday, February 21, 2020 - link

I think Intel will upgrade someday, but when they say 2021 that might really be more like 2023, 2024 or something if 10 nm is involved.For a long time I think Intel has starved their platform for I/O bandwidth. The press which is financed by Intel's advertising plus many victim users who've learned to blame themselves will deny that Intel's platform is bandwidth-starved, but it comes back to Intel's plan when Dempsey scaling ran out to eliminate other vendors from the BoM of laptops and desktop computers. In particular, the last thing they want you to do is get a good graphics card, or several of them. Don't you know that Intel Integrated Graphics are all you need?

On paper if you could really use all those PCIe lanes it wouldn't be so bad, but in real life you might find you have an i5 instead of an i7 or you might have a budget motherboard and practically you can't use all those lanes and you won't discover that until you try a year down the road. Building PCs nowadays seems worse than when you had to deal with IRQ conflicts on the ISA bus.

For a long time, Intel was trying to kill ATI and NVIDIA. NVIDIA was saved by deep learning and ethereum, whereas ATI merged with AMD and has been kept alive by APU sales for game consoles that keep alive the skills to make PC games for their chips.

Now Intel finally has parts that are too fast for PCI3 and they are changing their tune -- maybe even Xe will need something faster than a 2400 serial port when it finally comes out. But until now, Intel has wanted to crush anybody who makes hardware (except they've never tried to kill Synaptics, which I don't understand...)

mode_13h - Friday, February 21, 2020 - link

Uh, whatever.I think the reason Intel's server CPUs haven't had more PCIe lanes is that they support up to 8-socket configurations and saw deman for PCIe lanes as a way to move more CPUs. Big OEMs bought into this, too. Just try configuring a Dell server for a GPU - you'll quickly find that you can only do it in a dual-CPU configuration.