Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative

by Anton Shilov on December 5, 2018 12:00 PM EST- Posted in

- Storage

- CPUs

- SSDs

- Western Digital

- RISC-V

Western Digital this week made three important announcements concerning its RISC-V-based processor initiative launched last year. The company introduced its own SweRV general-purpose core, its OmniXtend cache coherency over Ethernet technology, and the open-sourced SweRV Instruction Set Simulator (ISS). Western Digital expects that the hardware and software will be used for various solutions aimed at Big Data and Fast Data applications, including flash controllers and SSDs.

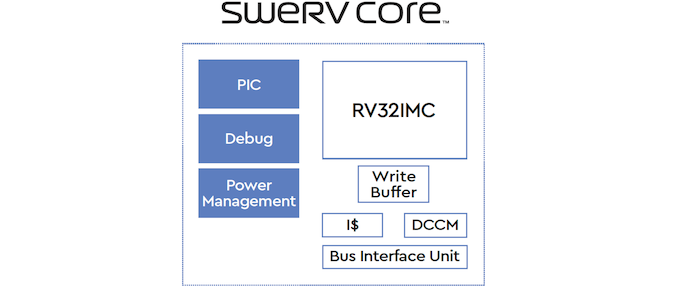

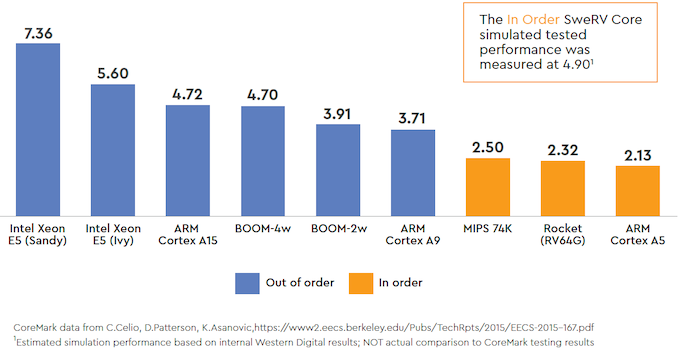

Western Digital’s RISC-V SweRV core is a 32-bit in-order core featuring a 2-way superscalar design and a nine-stage pipeline. When implemented using a 28 nm process technology, the core runs at up to 1.8 GHz. As for simulated performance, the SweRV core delivers 4.9 CoreMark/MHz, which is a bit higher when compared to ARM’s Cortex-A15. Western Digital will use its RISC-V cores for its own embedded designs, such as flash controllers and SSDs. The company will also make it available as an open-source product to third parties starting from Q1 2019. The company hopes that by enabling third-parties to use the core it will help to drive adoption of the RISC-V architecture by harware and software developers eventually.

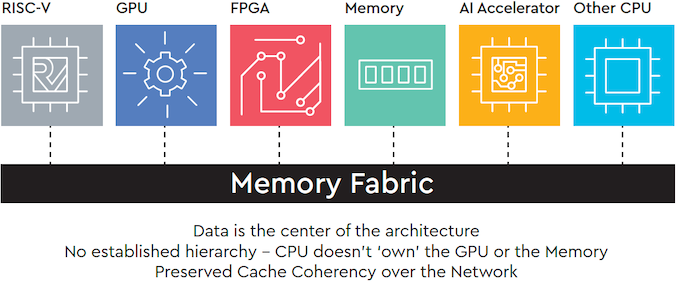

Along with its own CPU core, Western Digital is also rolling out its OmniXtend cache coherent memory technology, which enables cache coherence over Ethernet .Co-developed with SiFive, the company expects its OmniXtend tech to be used for attaching persistent memory to processors, but it says that this memory-centric architecture could be used for other components, including CPUs, GPUs, FPGAs, and machine learning accelerators.

Western Digital does not disclose maximum bandwidth its OmniXtend can provide but since we are dealing with Ethernet fabrics, it should not be slower than various versions of Ethernet in general. While the OmniXtend is open and available to various parties, it of course remains to be seen whether developers of the aforementioned components (accelerators, processors, etc.) actually decide to use the OmniXtend.

Finally, Western Digital also rolled outs its open-sourced SweRV Instruction Set Simulator (ISS). The program enables software designers to simulate execution of their code on the SweRV cores, simplifying development of programs, which is greatly important to drive adoption of RISC-V.

Related Reading:

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

- SiFive Unveils Freedom Platforms for RISC-V-Based Semi-Custom Chips

Source: Western Digital

11 Comments

View All Comments

JessicaLamb - Thursday, December 13, 2018 - link

Glad to see new improvements. Hope it will be useful for my project on https://writingpeak.co.uk/research-project-help High-quality data storage and processing is my priority